Approved

1442987G4C-A 10GBASE, XFP, ZR, TUNABLE TRANSCIEVER

## Features

- Compliant with XFP MSA

- Integrated OTN G.709 Digital Wrapper

- 6.2dB Net Coding Gain G-FEC for superior optical performance

- Tunability over full C-band 50GHz ITU-T wavelengths (SFF-8477 Control)

- Multi-protocol and bit rate support for 10GE, OC-192/STM-64, 10G FC and OTN

- Fully transparent 10G LAN PHY OTU2e at 11.09 Gbps

- Adaptive Receiver Decision Threshold Control for improved OSNR range

- True link BER reporting and Integrated PRBS 10 Gbps BERT for test set free link turn-up

- OTN Digital diagnostics and alarm reporting

# 1. Description

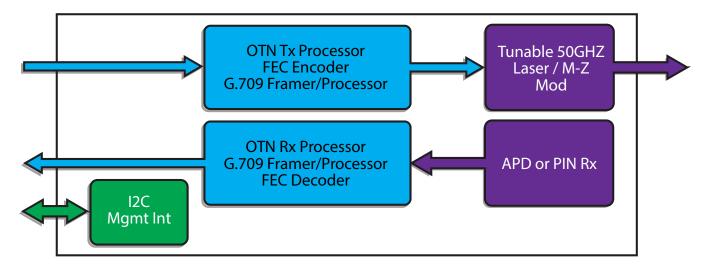

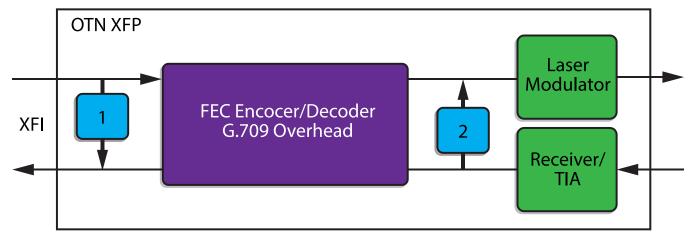

Approved Networks Tunable OTN XFP DWDM transceiver combines carrier grade OTN G.709 framing, FEC performance and 50GHz full C-band tunability into a XFP MSA compliant package. Approved Networks' Tunable OTN XFP is the only industry XFP MSA that can transparently carry a native 10G LAN PHY and SONET/SDH payload with a carriergrade DWDM Optical Transport Network (OTN) interface without the need for bandwidth limitation. OTN XFP combines a G.709 compliant Digital Wrapper and Forward Error Correction (FEC) with a M-Z modulated 50GHz tunable laser for superior optical performance and management functions equal to those found in external DWDM Transponder systems. Tunable OTN XFP is designed to interoperate with any Open DWDM line system that support 50GHz or 100GHzspaced wavelengths per the ITU-T C-band grid thus offering complete and cost effective DWDM transport for IP, MPLS, and Ethernet applications.

Tunable OTN XFP G.709 digital wrapper overhead and FEC functions are handled by the OTN Processor, which is integrated into the XFP module. The OTN Processor provides Operations Administration and Management (OAM) functions with G.709 alarms and Performance Management statistics.

# **Applications**

- IP/MPLS and Ethernet Switches

- Access, Metro and Regional Carrier Ethernet DWDM Networks

- MSPP

- Customer Premise Ethernet Demarcation

# 2. Management

Management of the Tunable OTN XFP is provided via the XFP MSA I2C interface, which supports digital diagnostic monitoring, alarms and loop backs to include G.709 and FEC management registers and wavelength tuning. Routers and Switches can reap the performance gains of FEC without changes to the existing I2C interface in a management Transparent Mode of operation, in which the Tunable OTN XFP activates the G.709 Digital Wrapper an FEC coding without the need for specific I2C provisioning.

# **3. Transceiver Optical Specifications**

| Parameter                                                                         | Symbol            | Min        | Typical                                                             | Мах      | Units      |  |

|-----------------------------------------------------------------------------------|-------------------|------------|---------------------------------------------------------------------|----------|------------|--|

| Host Native Nominal Bit Rate                                                      |                   |            | 3 (SONET/SDH<br>125 (LAN PHY                                        | -        | Gbps       |  |

| DWDM Line Interface Bit Rate                                                      |                   | 11.049 (   | 10.7092 (OTU2)<br>11.049 (OTU1e LAN PHY)<br>11.0957 (OTU2e LAN PHY) |          |            |  |

| OTN Interface Bit Rate Deviation                                                  |                   |            | +/- 20 (SONET)<br>+/- 100 (LAN PHY)                                 |          |            |  |

| DWDM Wavelength Range                                                             | λWDM              | 1528.38    | -                                                                   | 1565.50  | nm         |  |

| Channel Spacing                                                                   | fspacing          |            | 50                                                                  |          |            |  |

| Laser Tuning Range                                                                | ftune             | F          | Full C-band                                                         |          |            |  |

| Wavelength Accuracy                                                               | Δλεοl             | -25        | -                                                                   | +25      | pm         |  |

| Extinction Ratio                                                                  | ER                | 9          | -                                                                   | -        | dB         |  |

| Side Mode Suppression Ratio                                                       | SMSR              | 30         | -                                                                   | -        | dB         |  |

| Average Output Power                                                              | POUT              | 0          | -                                                                   | +3       | dBm        |  |

| Eye Mask Compliance                                                               |                   | GR-2       | GR-253i3/G.959.1                                                    |          |            |  |

| Receiver Operating Range @<br>11.1Gbps 0ps/nm Dispersion<br>+1400ps/nm Dispersion | PIN<br>(80km APD) | -28<br>-25 | -                                                                   | -7<br>-7 | dBm<br>dBm |  |

| Parameter                                                                                              | Symbol                | Min        | Typical      | Мах     | Units        |

|--------------------------------------------------------------------------------------------------------|-----------------------|------------|--------------|---------|--------------|

| Receiver Operating Range @<br>11.1Gbps 0ps/nm Dispersion<br>+1400ps/nm Dispersion                      | PIN<br>(40km PIN)     | -18<br>-16 | -            | 0<br>-2 | dBm<br>dBm   |

| OSNR Requirement @ 11.1Gbps<br>0 ps/nm -500ps/nm to +1300ps/<br>nm Dispersion -18dBm to -8dBm<br>Input | OSNRMIN<br>(80km APD) | 16<br>20   | -            | -       | dB/<br>0.1nm |

| OSNR Requirement @ 11.1Gbps<br>0 ps/nm +800ps/nm Dispersion<br>-12dBm to -1dBm Input                   | OSNRMIN<br>(40km PIN) | 15.5<br>19 | -            | -       | dB/<br>0.1nm |

| Jitter Compliance                                                                                      | -                     | 802.       | 3ae/GR-253i3 |         |              |

| Operating Case Temperature                                                                             | TC                    | -10        | -            | 85      | °C           |

| Storage Temperature                                                                                    | Tstg                  | -40        | -            | 85      | °C           |

# 4. PRBS-31 "True Link" Pattern Generator and Checker

The OTN XFP "True Link" feature consists of a PRBS-31 Generator and Checker to allow the customer to determine the 11Gbps channel performance without the need for costly 10GE or OC-192 payload test equipment. In the transmit direction a PRBS-31 pattern is generated and inserted into the OTU-2 payload portion of the frame. The OTU-2, ODU-2 and FEC data is generated and monitored normally to allow for link alarming and FEC correction performance monitoring. A status bit it provided to the user to denote PRBS-31 pattern synchronization. In the receive direction, the PRBS-31 payload is decoded and checked for individual bit level errors. A PRBS-31 payload error counter is provided via the OTN XFP standard I2C interface.

The following I2C registers are used for the True Link feature:

| Page | Reg | Bit | Туре    | Title       | Description                                           | Settings                                                                                                   |

|------|-----|-----|---------|-------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 03h  | 183 | 7   | R/W, SC | PRBS31      | PRBS-31 error<br>counter reset (Self<br>Clearing Bit) | 1 = Reset PRBS-31 error<br>counter<br>(This bit is self clearing back<br>to zero)<br>0 = Normal operation. |

| 03h  | 183 | 5:6 | R/W     | Control     | Reserved                                              |                                                                                                            |

| 03h  | 183 | 4   | RO      | (Line Side) | PRBS31 sync status                                    | 0 = PRBS-31 Rx pattern sync<br>present<br>1 = PRBS-31 Rx pattern sync<br>error                             |

| 03h  | 183 | 2:3 | R/W     |             | Reserved                                              |                                                                                                            |

| Page | Reg | Bit | Туре | Title | Description                         | Settings                                                                                                                                                                                                                                                                   |

|------|-----|-----|------|-------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03h  | 183 | 1   | R/W  |       | Enable PRBS31<br>pattern on Rx Path | <ul> <li>1 = Enable PRBS31 payload</li> <li>read in the Rx direction. If</li> <li>FEC enabled, PRBS31 is error</li> <li>corrected. If FEC is off, PRBS1</li> <li>raw data is sent.</li> <li>0 = Disable PRBS31 payload</li> <li>read in the Rx direction.</li> </ul>       |

| 03h  | 183 | 0   | R/W  |       | Enable PRBS31<br>pattern on Tx Path | <ul> <li>1 = Enable PRBS31 payload</li> <li>insertion in the Tx direction.</li> <li>The Tx direction PRBS data is</li> <li>inserted as the payload data</li> <li>in the OTU2 frame.</li> <li>0 = Disable PRBS31 payload</li> <li>insertion in the Rx direction.</li> </ul> |

| Page | Reg | Bit | Туре | Title Description                |                                                         | Settings                                            |

|------|-----|-----|------|----------------------------------|---------------------------------------------------------|-----------------------------------------------------|

| 03h  | 184 | 7:0 | RO   | PRBS31<br>Checker<br>(Line Side) | PRBS31 Error Counter<br>(MSB- 32 bit counter)           | PRBS31 Error Count<br>(MSB- 32 bit)                 |

| 03h  | 185 | 7:0 | RO   |                                  | PRBS31 Error Counter<br>(17 to 24 of 32 bit<br>counter) | PRBS31 Error Count<br>(17 to 24 of 32 bit counter). |

| 03h  | 186 | 7:0 | RO   |                                  | PRBS31 Error Counter<br>(8 to 16 of 32 bit<br>counter)  | PRBS31 Error Count<br>(8 to 16 of 32 bit counter)   |

| 03h  | 187 | 7:0 | RO   |                                  | PRBS31 Error Counter<br>(LSB- 32 bit counter)           | PRBS31 Error Count (<br>LSB- 32 bit).               |

# 5. Link Checker Feature

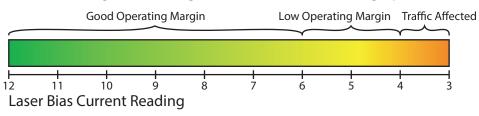

The OTN XFP has the optional "Link Checker" feature, allowing the customer to proactively monitor the link performance margin in real time locally or remotely. Link Checker provides proactive alarms to alert the customer of a link falling below a pre-defined margin threshold, triggering an investigation of the optical layer to rectify the degradation before the customer takes errors. The user monitors Laser Bias Current to verify the health or margin on the OTN wavelength. The Link Checker margin can vary between 3 and 12, in which the higher the number the higher the margin. This is illustrated in the graph below.

As seen an OTN XFP DWDM channel with a Link Checker reading of 6 or higher is operating with a good operating margin. Between 4 and 6 the link margin is low and may be the indicator of a link problem on the DWDM system. At 4 or below traffic is affected or down on that link.

The link margin is supported through the reading of the FEC Correction Error Rate (FCER) in the XFP and displaying that margin as the Laser Bias Current value on the router. The FEC correction error rate is averaged over a 25 second rolling window by the module software. In the case of failure or no errors being corrected, the correction error rate is shown as 12.

The transposition of the correction error rate to laser bias current is shown below: The FEC Correction BER can be represented as:

xx = Mantissa yy = Exponent

For example, an error correction error rate of 3x10-6 where the Mantissa xx = 3 and the Exponent yy = 6

The Laser Bias Current on the router is then shown as = yy.xx mA

Therefore a FEC Correction Error Rate (FCER) of 3x10-6 is shown as a Laser Bias current of 6.3 mA Any error rate <10-5 will raise a Laser Bias Low Alarm in the system, which is an early warning indicator to the NOC to proactively monitor and correct for a degraded link before errors are seen by the customer.

#### 6. OTN XFP Loopbacks

OTN XFP supports both host and line loopbacks. The host loopback is designed to loopback traffic towards the host before processing by the FEC and G.709 overhead processor in the OTN XFP module. A line loopback loops the traffic towards the OTN fiber network before processing the FEC and G.709 overhead. Both loopbacks are completed in the FEC/G.709 ASIC. All loopbacks are supported via the I2C interface.

The following loopbacks are supported:

1. Host Loopback (towards host). This is referred to as the XFI loopback in the XFF MSA Rev 4.5.

2. Line Loopback (towards OTN fiber network)

The XFP loopback settings are controlled according to the MSA XFP I2C interface using the following registers:

| Table | Reg | Bits | Туре | Category    | <b>Register Item</b>  | Feature Notes                                                          |  |

|-------|-----|------|------|-------------|-----------------------|------------------------------------------------------------------------|--|

| Any   | 1   | 2    | R/W  | Signal      | Line Side<br>Loopback | 0 = Normal Operation<br>1 = Loopback Module Optical Input to<br>Output |  |

| Any   | 1   | 1    |      | Conditioner | XFI Loopback          | 0 = Normal Operation<br>1 = Loopback Module XFI Input to<br>Output     |  |

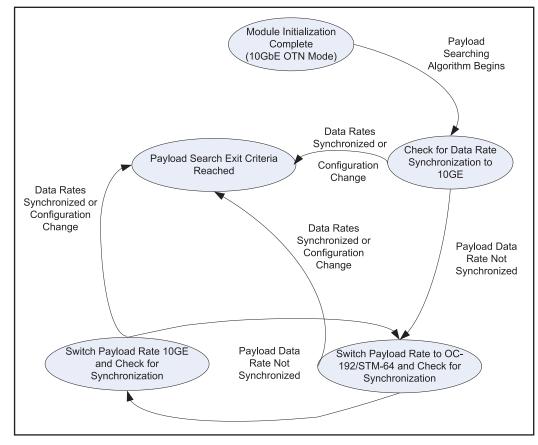

### 7. Startup Autonomous Payload Searching

OTN XFP supports a payload search feature when the module is initially powered up or reset. The Payload Search feature is only valid in OTN mode and is run to select the correct payload data rate for the module if the host does not select the value in the XFP Signal Conditioner register. Since the OTN XFP contains PLLs and reference clocks centered on the exact OTN output bit rate, the module must be configured in the correct payload bit rate mode for proper operation. A module not configured correctly cannot pass traffic. The Payload Search mode works in the following steps:

- 1. Upon module initialization or reset completion, the module default configuration is 10GE LAN PHY (10.3125Gbps) with OTN enabled (11.1Gbps). When the module exists the initialization stage, an internal check is performed on the incoming host side data to see if the payload data rate matches the configured 10GE (10.3125Gbps) data rate.

- 2. If the module is not able to synchronize to the default configuration data rate of 10GE (10.3125Gbps) with the incoming host data, the module is automatically configured by the firmware to a data rate of OC-192/STM-64 (9.953Gbps) and timing synchronization is checked again.

- 3. If after step 2 the data rate of the incoming host data is not synchronized to the payload data rate, the module will continue switching between 10GE and OC-192/STM-64 data rates until a synchronization of payload data rate occurs. The time between switches is about 5 seconds. If no input electrical XFI signal is present on the host input side, the Payload Searching algorithm is frozen and resumed when data is detected.

- 4. If at any time during Step 1. through Step 3. the payload data is correctly synchronized to the module settings, the Autonomous Payload Searching loop is exited. During the Payload Searching algorithm the laser output is disabled and the module is held in a MOD\_NR state. The data rate setting of the Signal Conditioner register [1.7:4] will display the OTN XFP current payload data rate setting.

The following conditions force the module to exit the Autonomous Payload Searching algorithm:

| Condition                                 | Description                                                                                | Notes                                                                                   |

|-------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Host Payload Sync<br>to Module Settings   | The host input electrical XFI data rate matches the module payload data rate configuration | Host data must be<br>present                                                            |

| Signal Conditioner<br>Register is written | Lower Memory Register 1 is written                                                         | Signifies host is writing<br>data rate value in I2C<br>Register                         |

| OTN Setup Register<br>1 is written        | Register [03,128] is written                                                               | Signifies host is writing<br>OTN configuration<br>change, which can<br>affect data rate |

| Payload Search is<br>Disabled             | Register [03,192.2] is written to '0'                                                      | Host disabled the<br>Payload Search via I2C                                             |

The following state diagram explains the Autonomous Payload Search operation:

Figure 1. Autonomous Payload Searching Algorithm State Machine

#### Note:

During the Autonomous Payload Searching algorithm, the PM error counters and the PM time counter is delayed due to extra processor power required to support the Payload Search algorithm. Once the payload search algorithm is completed, the host should normalize the PM error and time counters as part of the OTN XFP initialization process.

#### 8. Laser Safety

OTN XFP is compliant to IEC 60825-1 laser safety. The DWDM laser output is specified as a Class 1 output power as defined in IEC 60825-1, ed 2.0 2007.

**CAUTION** – Use of controls or adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

#### 9. Maximum Power Ratings

OTN XFP power rail draw is shown below for Tunable DWDM XFP with 70° case temperature:

| Parameter          | Voltage | Мах  | Unit |

|--------------------|---------|------|------|

| +5V Current        | F       | 210  | mA   |

| 5V Power           | 5 -     | 1.05 | W    |

| +1.8V Current      | 1.0     | 735  | mA   |

| +1.8V Power        | 1.8     | 1.32 | W    |

| +3.3V Current      |         | 575  | mA   |

| +3.3V Power        | 3.3     | 1.90 | W    |

| Total Module Power |         | 4.27 | W    |

# 10. DOM Alarm Thresholds and I2C Locations

All Alarm Thresholds for OTN XFP are configured at the manufacturer and cannot be configured through the I2C interface (i.e. thresholds are not provisionable). Alarm thresholds for each DOM parameter are located in the following registers.

| Threshold Value<br>Register | Latched<br>Alarm | Threshold Size<br>(Bytes) | Name                             |

|-----------------------------|------------------|---------------------------|----------------------------------|

| 02-03                       | 80.7             | 2                         | Transceiver Temp High Alarm      |

| 04-05                       | 80.6             | 2                         | Transceiver Temp Low Alarm       |

| 06-07                       | 82.7             | 2                         | Transceiver Temp High Warning    |

| 08-09                       | 82.6             | 2                         | Transceiver Temp Low Warning     |

| 10-17                       | N/A              | 8                         | Reserved                         |

| 18-19                       | 80.3             | 2                         | Laser Bias Current High Alarm    |

| 20-21                       | 80.2             | 2                         | Laser Bias Current Low Alarm     |

| 22-23                       | 82.3             | 2                         | Laser Bias Current High Warning  |

| 24-25                       | 82.2             | 2                         | Laser Bias Current Low Warning   |

| 26-27                       | 80.1             | 2                         | Laser Output Power High Alarm    |

| 28-29                       | 80.0             | 2                         | Laser Output Power Low Alarm     |

| 30-31                       | 82.1             | 2                         | Laser Output Power High Warning  |

| 32-33                       | 82.0             | 2                         | Laser Output Power Low Warning   |

| 34-35                       | 81.7             | 2                         | Receive Optical Power High Alarm |

| Threshold Value<br>Register | Latched<br>Alarm | Threshold Size<br>(Bytes) | Name                               |

|-----------------------------|------------------|---------------------------|------------------------------------|

| 36-37                       | 81.6             | 2                         | Receive Optical Power Low Alarm    |

| 38-39                       | 83.7             | 2                         | Receive Optical Power High Warning |

| 40-41                       | 83.6             | 2                         | Receive Optical Power Low Warning  |

|                             | 86.7             |                           | 5V High Alarm                      |

|                             | 86.6             |                           | 5V Low Alarm                       |

|                             | 86.5             |                           | 3.3V High Alarm                    |

|                             | 86.4             |                           | 3.3V Low Alarm                     |

|                             | 86.3             |                           | 1.8V High Alarm                    |

|                             | 86.2             |                           | 1.8V Low Alarm                     |

| N1/A                        | 86.1             | N/A                       | -5V High Alarm (Not Used)          |

| N/A                         | 86.0             | N/A                       | -5V Low Alarm (Not Used)           |

|                             | 87.7             |                           | 5V High Warning                    |

|                             | 87.6             |                           | 5V Low Warning                     |

|                             | 87.5             |                           | 3.3V High Warning                  |

|                             | 87.4             |                           | 3.3V Low Warning                   |

|                             | 87.3             |                           | 1.8V High Warning                  |

|                             | 87.2             |                           | 1.8V Low Warning                   |

# 11. Pin Descriptions

| Towards ASIC | 16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 |  | GND<br>RD+<br>GND<br>VCC2<br>P_DOV<br>VCC2<br>GND<br>REFCLH<br>GND<br>GND<br>TD-<br>TD+<br>GND | VCC3<br>VCC3<br>GND<br>K+ VCC5 |  | 15<br>14<br>13<br>12<br>11<br>10<br>9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1 | Towards Bezel |

|--------------|----------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------|--------------------------------|--|-------------------------------------------------------------------------------|---------------|

|--------------|----------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------|--------------------------------|--|-------------------------------------------------------------------------------|---------------|

| Pin | Logic      | Symbol         | Name/Description                                                                                                                                                                                                                                                                     | Notes |

|-----|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1   |            | GND            | Module Ground                                                                                                                                                                                                                                                                        | 1     |

| 2   |            | VEE5           | Optional –5.2 Power Supply – Not required                                                                                                                                                                                                                                            |       |

| 3   | LVTTL-I    | Mod-Desel      | Module De-select; When held low allows the module to, respond to 2-wire serial interface commands                                                                                                                                                                                    |       |

| 4   | LVTTL-O    | Interrupt      | Interrupt (bar); Indicates presence of an important condition which can be read over the serial 2-wire interface                                                                                                                                                                     | 2     |

| 5   | LVTTL-I    | TX_DIS         | Transmitter Disable; Transmitter laser source turned off                                                                                                                                                                                                                             |       |

| 6   |            | VCC5           | +5 Power Supply – Not required                                                                                                                                                                                                                                                       |       |

| 7   |            | GND            | Module Ground                                                                                                                                                                                                                                                                        |       |

| 8   |            | VCC3           | +3.3V Power Supply                                                                                                                                                                                                                                                                   |       |

| 9   |            | VCC3           | +3.3V Power Supply                                                                                                                                                                                                                                                                   |       |

| 10  | LVTTL-I    | SCL            | Serial 2-wire interface clock                                                                                                                                                                                                                                                        | 2     |

| 11  | LVTTL- I/O | SDA            | Serial 2-wire interface data line                                                                                                                                                                                                                                                    | 2     |

| 12  | LVTTL-O    | Mod_Abs        | Module Absent; Indicates module is not present. Grounded in the module.                                                                                                                                                                                                              | 2     |

| 13  | LVTTL-O    | Mod_NR         | Module Not Ready;                                                                                                                                                                                                                                                                    | 2     |

| 14  | LVTTL-O    | RX_LOS         | Receiver Loss of Signal indicator                                                                                                                                                                                                                                                    | 2     |

| 15  |            | GND            | Module Ground                                                                                                                                                                                                                                                                        | 1     |

| 16  |            | GND            | Module Ground                                                                                                                                                                                                                                                                        | 1     |

| 17  | CML-O      | RD-            | Receiver inverted data output                                                                                                                                                                                                                                                        |       |

| 18  | CML-O      | RD+            | Receiver non-inverted data output                                                                                                                                                                                                                                                    |       |

| 19  |            | GND            | Module Ground                                                                                                                                                                                                                                                                        | 1     |

| 20  |            | VCC2           | +1.8V Power Supply – Not required                                                                                                                                                                                                                                                    | 3     |

| 21  | LVTTL-I    | P_Down/<br>RST | Power Down; When high, places the module in the low<br>power stand-by mode and on the falling edge of P_Down<br>initiates a module reset. Reset; The falling edge initiates a<br>complete reset of the module including the 2-wire serial<br>interface, equivalent to a power cycle. |       |

| 22  |            | VCC2           | +1.8V Power Supply – Not required                                                                                                                                                                                                                                                    | 3     |

| 23  |            | GND            | Module Ground                                                                                                                                                                                                                                                                        | 1     |

| 24  | PECL-I     | RefCLK+        | Reference Clock non-inverted input, AC coupled on the host board                                                                                                                                                                                                                     |       |

| 25  | PECL-I     | RefCLK-        | Reference Clock inverted input, AC coupled on the host board                                                                                                                                                                                                                         |       |

| 26  |            | GND            | Module Ground                                                                                                                                                                                                                                                                        | 1     |

| 27  |            | GND            | Module Ground                                                                                                                                                                                                                                                                        | 1     |

| 28  | CML-I      | TD-            | Transmitter inverted data input                                                                                                                                                                                                                                                      |       |

| 29  | CML-I      | TD+            | Transmitter non-inverted data input                                                                                                                                                                                                                                                  |       |

| 30  |            | GND            | Module Ground                                                                                                                                                                                                                                                                        | 1     |

#### Notes:

- 1. Module ground pins (GND) are isolated from the module case and chassis ground within the module.

- 2. Shall be pulled up with 4.7K-10K ohms to a voltage between 3.15V and 3.45V on the host board.

## 12. Wavelengths Supported

| Frequency | Wavelength | Frequency | Wavelength | Frequency | Wavelength |

|-----------|------------|-----------|------------|-----------|------------|

| 196.15    | 1528.38    | 196.10    | 1528.77    | 196.05    | 1529.16    |

| 196.00    | 1529.55    | 195.95    | 1529.94    | 195.90    | 1530.33    |

| 195.85    | 1530.72    | 195.80    | 1531.12    | 195.75    | 1531.51    |

| 195.70    | 1531.90    | 195.65    | 1532.29    | 195.60    | 1532.68    |

| 195.55    | 1533.07    | 195.50    | 1533.47    | 195.45    | 1533.86    |

| 195.40    | 1534.25    | 195.35    | 1534.64    | 195.30    | 1535.04    |

| 195.25    | 1535.43    | 195.20    | 1535.82    | 195.15    | 1536.22    |

| 195.10    | 1536.61    | 195.05    | 1537.00    | 195.00    | 1537.40    |

| 194.95    | 1537.79    | 194.90    | 1538.19    | 194.85    | 1538.58    |

| 194.80    | 1538.98    | 194.75    | 1539.37    | 194.70    | 1539.77    |

| 194.65    | 1540.16    | 194.60    | 1540.56    | 194.55    | 1540.95    |

| 194.50    | 1541.35    | 194.45    | 1541.75    | 194.40    | 1542.14    |

| 194.35    | 1542.54    | 194.30    | 1542.94    | 194.25    | 1543.33    |

| 194.20    | 1543.73    | 194.15    | 1544.13    | 194.10    | 1544.53    |

| 194.05    | 1544.92    | 194.00    | 1545.32    | 193.95    | 1545.72    |

| 193.90    | 1546.12    | 193.85    | 1546.52    | 193.80    | 1546.92    |

| 193.75    | 1547.32    | 193.70    | 1547.72    | 193.65    | 1548.11    |

| 193.60    | 1548.51    | 193.55    | 1548.91    | 193.50    | 1549.32    |

| 193.45    | 1549.72    | 193.40    | 1550.12    | 193.35    | 1550.52    |

| 193.30    | 1550.92    | 193.25    | 1551.32    | 193.20    | 1551.72    |

| 193.15    | 1552.12    | 193.10    | 1552.52    | 193.05    | 1552.93    |

| 193.00    | 1553.33    | 192.95    | 1553.73    | 192.90    | 1554.13    |

| 192.85    | 1554.54    | 192.80    | 1554.94    | 192.75    | 1555.34    |

| 192.70    | 1555.75    | 192.65    | 1556.15    | 192.60    | 1556.55    |

| 192.55    | 1556.96    | 192.50    | 1557.36    | 192.45    | 1557.77    |

| 192.40    | 1558.17    | 192.35    | 1558.58    | 192.30    | 1558.98    |

| 192.25    | 1559.39    | 192.20    | 1559.79    | 192.15    | 1560.20    |

| 192.10    | 1560.61    | 192.05    | 1561.01    | 192.00    | 1561.42    |

| 191.95    | 1561.83    | 191.90    | 1562.23    | 191.85    | 1562.64    |

| 191.80    | 1563.05    | 191.75    | 1563.45    | 191.70    | 1563.86    |

| 191.65    | 1564.27    | 191.60    | 1564.68    | 191.55    | 1565.09    |

| 191.50    | 1565.50    |           |            |           |            |

Approved Networks, Inc.

# **13. Contact Information**

Approved Networks is a leading supplier of Network Transceivers and Connectivity products to Channel Partners, Resellers, and OEMs. With more than 9 years of direct industry experience, our products are resident in the most demanding and mission critical functional networks Worldwide. We serve as a Master Distributor to the largest CMs in the world and deploy the most rigorous testing and firmware management programs to bring the highest level of functional product to the market at a cost that makes sense.

Corporate Offices: **Approved Networks, Inc.** Tel: 800.590.9535 Web: http://www.approvednetworks.com